射頻集成電路原理設計 從基礎理論到現代應用

射頻集成電路(RFIC)是現代無線通信系統的核心,它將射頻信號處理功能集成在單一芯片上,廣泛應用于手機、Wi-Fi、藍牙、雷達和衛星通信等領域。射頻集成電路設計融合了半導體工藝、電路理論和電磁場理論,是一項高度復雜且專業的技術。

一、射頻集成電路的基本原理

射頻集成電路工作在數百MHz至數十GHz的頻率范圍內,其設計需要遵循獨特的原理:

- 阻抗匹配:在射頻領域,阻抗不匹配會導致信號反射和功率損失。設計時必須確保信號源、傳輸線和負載之間的阻抗匹配,通常采用無源元件(如電感和電容)構成匹配網絡,以最大化功率傳輸。

- 噪聲系數:射頻電路對噪聲非常敏感,噪聲系數(NF)衡量了電路引入的附加噪聲。低噪聲放大器(LNA)的設計需優先考慮最小化噪聲系數,以提高接收機的靈敏度。

- 線性度:射頻放大器等組件需在高功率信號下保持良好的線性度,以避免諧波失真和互調失真。常用指標包括1dB壓縮點(P1dB)和三階交調點(IP3)。

- 穩定性:射頻電路可能在某些頻率下產生振蕩,設計時必須進行穩定性分析,通常通過K-Δ測試或穩定性圓來確保電路在所有條件下穩定工作。

二、射頻集成電路的關鍵模塊設計

- 低噪聲放大器(LNA):作為接收機前端,LNA需在放大微弱信號的同時引入最小噪聲。設計時需權衡噪聲系數、增益、線性度和阻抗匹配。常用拓撲包括共源極、共柵極和共源共柵結構。

- 混頻器:混頻器將射頻信號下變頻為中頻信號,或反之。設計需關注轉換增益、噪聲系數、線性度和端口隔離度。吉爾伯特單元(Gilbert Cell)是集成混頻器的常見結構。

- 壓控振蕩器(VCO):VCO產生可調頻率的本地振蕩信號,其設計核心是諧振電路(如LC諧振腔)和變容二極管。關鍵指標包括相位噪聲、調諧范圍和功耗。

- 功率放大器(PA):PA將信號放大到足夠功率以驅動天線,設計需平衡效率、線性度和輸出功率。常用技術包括Doherty放大器和開關模式放大器(如Class E)。

三、集成電路設計流程與技術挑戰

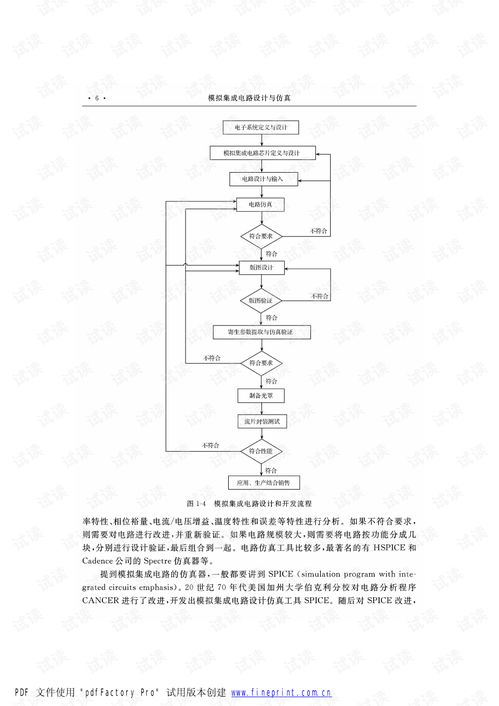

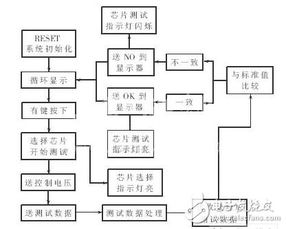

- 設計流程:射頻IC設計遵循標準流程:首先根據系統指標確定架構,然后進行電路設計和仿真(使用ADS、Cadence等工具),接著進行版圖設計,最后進行流片和測試。

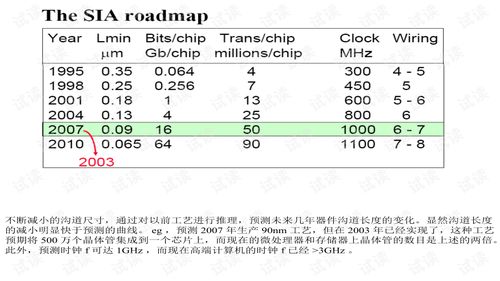

- 工藝選擇:射頻IC常用工藝包括硅基CMOS、SiGe BiCMOS和GaAs。CMOS工藝成本低、集成度高,適合大規模生產;GaAs性能優異但成本高,適用于高頻應用。

- 寄生效應:在高頻下,寄生電容、電感和襯底耦合會顯著影響性能。版圖設計時需采用屏蔽、隔離和對稱布局等技術來減小寄生效應。

- 系統集成:現代射頻IC往往集成數字基帶和射頻前端,形成系統級芯片(SoC)。這帶來了數模混合信號干擾、電源噪聲等挑戰,需通過協同設計和隔離技術解決。

四、未來發展趨勢

隨著5G/6G通信、物聯網和毫米波雷達的興起,射頻集成電路正朝著更高頻率、更低功耗和更高集成度的方向發展。新技術如硅基毫米波電路、可重構射頻前端和異構集成(將不同工藝芯片封裝在一起)將成為未來研究熱點。

射頻集成電路設計是一門融合多學科知識的藝術,它不斷推動著無線通信技術的革新。設計師需深入理解射頻原理,掌握先進工具,并緊跟工藝發展,才能創造出高性能、高可靠性的射頻芯片。

如若轉載,請注明出處:http://www.fromschool.cn/product/67.html

更新時間:2026-01-20 08:02:41