中規模集成電路功能測試儀設計方案詳解

中規模集成電路(MSI)功能測試儀是電子工程領域進行芯片驗證、故障排查和質量控制的關鍵設備。它介于簡單的數字萬用表與復雜昂貴的全自動測試設備(ATE)之間,專門針對包含計數器、寄存器、譯碼器、數據選擇器等常見MSI芯片的邏輯功能進行高效、準確的測試。一個完整的設計方案需要綜合考慮系統架構、硬件電路、軟件控制以及人機交互等多個方面。

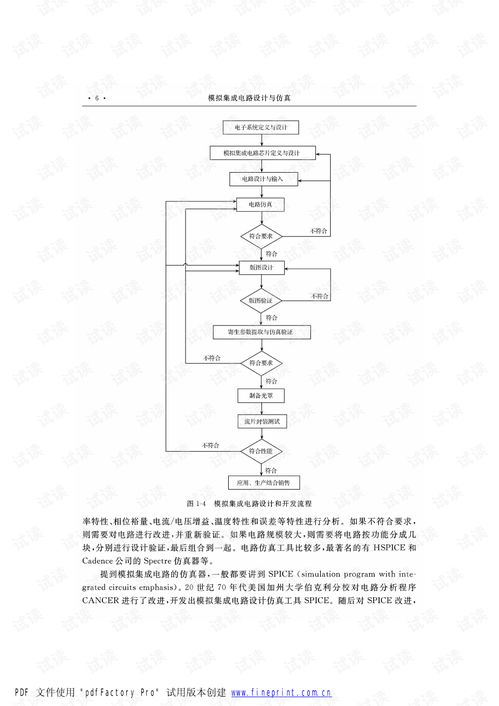

一、 系統總體架構設計

典型的MSI功能測試儀采用“主控單元+測試適配器”的模塊化架構。

- 主控單元:通常以微控制器(如STM32系列)或FPGA為核心,負責整個測試流程的協調控制、測試向量的生成與施加、響應信號的采集與比較,以及最終結果的判定與輸出。

- 測試向量生成與施加模塊:根據被測芯片(DUT)的真值表或功能時序圖,預先編制或動態生成所有需要測試的輸入邏輯組合(測試向量),并通過驅動電路施加到DUT的對應引腳。

- 響應采集與比較模塊:同步采集DUT在測試向量激勵下的實際輸出,與存儲在儀器內的預期輸出(黃金標準)進行逐位比較。

- 測試適配器(接口夾具):作為與被測芯片的物理連接界面,通常采用零插拔力(ZIF)插座,并針對不同封裝(如DIP、SOP)設計可更換的適配頭,以提高儀器的通用性。

- 人機交互界面:包括LCD顯示屏、鍵盤或觸摸屏,用于選擇芯片型號、啟動測試、顯示測試進度和結果(通過/失敗,及具體故障點)。

二、 關鍵硬件電路設計詳解

- 微控制器/FPGA選型與最小系統:選擇具備足夠I/O引腳數量、處理速度和存儲空間的控制器。FPGA在并行生成復雜時序向量方面具有優勢,而MCU在成本和控制靈活性上更佳。需設計穩定的電源、時鐘和復位電路。

- 引腳驅動電路:為確保能可靠地驅動DUT的輸入引腳(尤其是需要拉高或拉低),通常使用數字緩沖器(如74HC244)來增強MCU/FPGA I/O口的驅動能力,并可能包含電平轉換電路以適應不同邏輯家族(如TTL、CMOS)的芯片。

- 響應采集電路:DUT的輸出信號通過緩沖器或直接接入MCU/FPGA的I/O口進行讀取。對于高速信號,需考慮信號完整性。關鍵節點可設計測試點,方便調試。

- 電源管理模塊:為DUT提供精確、可調且干凈的直流電源(如+5V, ±12V等),并具備過流、過壓保護功能,防止損壞昂貴芯片。

- 通信接口:設計USB或以太網接口,用于從上位機下載測試程序、更新芯片庫,以及上傳測試數據。

三、 軟件與測試算法設計

- 芯片數據庫:建立完善的MSI芯片數據庫,記錄每種芯片的引腳定義、功能真值表/時序、推薦工作電壓、測試向量集等。

- 測試向量生成算法:

- 窮舉法:對于輸入引腳數較少的芯片,生成所有可能的輸入組合進行全覆蓋測試。

- 功能路徑法:針對復雜功能,根據其功能描述(如計數、移位)生成能遍歷所有關鍵狀態的測試序列,在保證覆蓋率的同時提高測試效率。

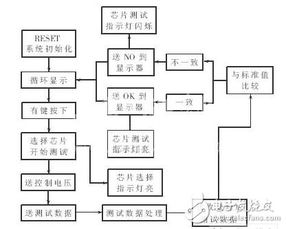

- 主控程序流程:上電初始化 -> 操作員選擇芯片型號 -> 系統自動配置電源及I/O映射 -> 加載對應測試向量集 -> 逐條施加向量并采集響應 -> 實時比較判斷 -> 生成并顯示測試報告。

- 故障診斷輔助:測試失敗時,不僅能報告“不合格”,還應能定位到是哪個輸入組合下、哪個輸出引腳的實際響應與預期不符,極大輔助維修人員分析是芯片故障還是外圍電路問題。

四、 方案特點與優化考慮

- 高性價比:針對MSI芯片測試需求定制,避免了ATE的冗余功能和過高成本。

- 操作簡便:自動化測試流程,無需使用者深諳芯片內部原理,降低了對操作人員的技術要求。

- 擴展性強:模塊化設計使得通過更新適配器和芯片數據庫,即可支持新的芯片型號。

- 優化方向:可考慮加入模擬功能測試(如運放的增益、帶寬測量)、三態輸出測試、以及基于邊界掃描(JTAG)技術的更深入測試,以覆蓋更復雜的芯片。

一個優秀的中規模集成電路功能測試儀設計方案,是硬件可靠性、軟件智能性和人機交互友好性的緊密結合。它通過自動化的功能驗證,成為集成電路研發、生產、教學和維修環節中提升效率、保障質量不可或缺的工具。

如若轉載,請注明出處:http://www.fromschool.cn/product/68.html

更新時間:2026-01-20 04:12:13